周边元件互连(Peripheral Component Interconnect,PCI)标准组织PCI-SIG本周公布了PCIe 8.0标准草案,预计2028年正式发布给产业,最高数据传输率可达1.0 TB/s。最新发布的PCIe 8.0标准草案为0.5版,预计在2028年向产业界开放。

PCIe SIG指出,PCIe 8.0规格旨在提供高扩展性的互连方案,以支持新兴应用,包括人工智能、机器学习、高速网络、边缘计算与量子计算,并将服务于数据密集型市场,如汽车、超大规模数据中心、高性能计算(HPC)及军工/航空航天领域。

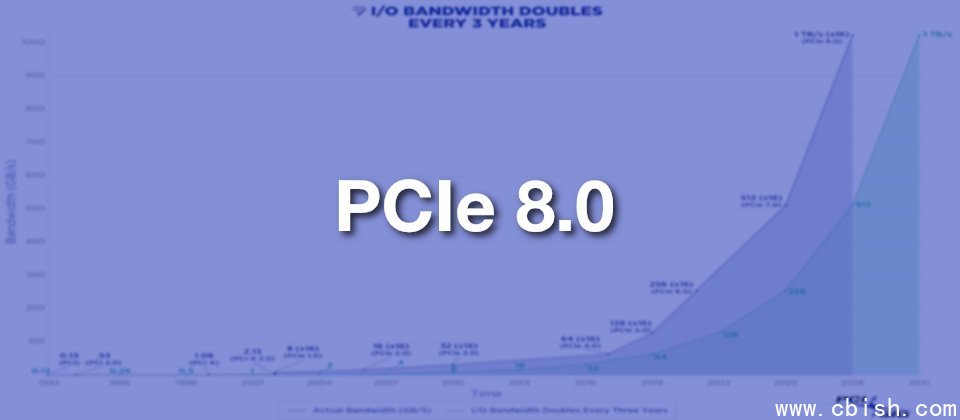

技术规格方面,PCIe 8.0延续过去几代每三年速率翻倍的更新节奏。其单通道(Lane)的原始比特率,较2025年6月发布的PCIe 7.0的128 GT/s提升一倍,达到256 GT/s。单向带宽从上一代的16 GB/s提升至32 GB/s。在x16配置下,双向总带宽可达1,024 GB/s,突破1 TB/s。

PCIe 8.0的制定目标不仅限于提升传输速度,还计划改进连接器设计、降低延迟、提升稳定性、提高有效带宽利用率、降低功耗等。PCIe 6/7/8已采用PAM4(四电平脉冲幅度调制)信号技术,但该技术存在抗干扰能力下降、误码率(BER)升高的问题。PCI-SIG暗示正在评估新型连接器技术,据Tom's Hardware报道,可能引入光互连的光学感知重定时器(optical-aware retimer)架构。

为应对PAM4带来的误码问题,PCIe已引入前向纠错(Forward Error Correction,FEC)技术,但该技术会增加延迟。因此,PCIe 8.0希望在提升通信可靠性的同时,兼顾低延迟目标。

PCIe 8.0还计划通过基于FLIT的编码与错误管理机制,进一步提升有效带宽利用率。此外,随着人工智能与高性能计算应用对功耗需求的持续增长,PCIe 8.0有望通过更高效的SerDes(串行器/解串器)、编码方案与电源管理技术降低能耗。最后,一如以往标准,PCIe 8.0将继续保持与前代版本的向后兼容性。