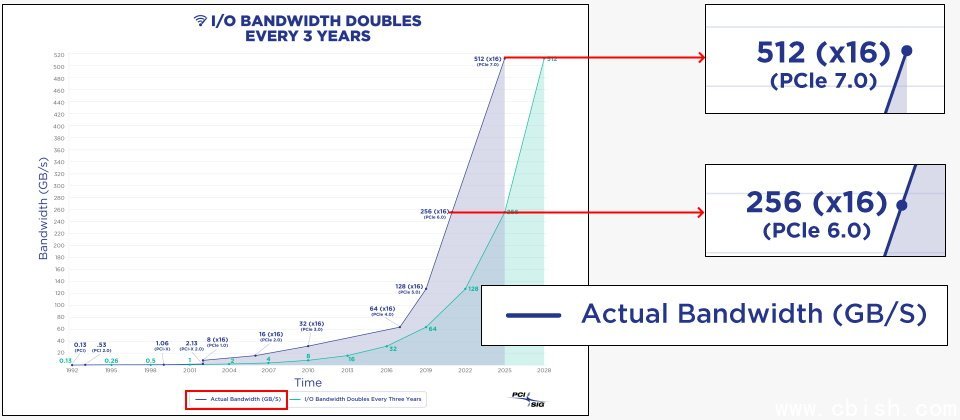

PCIe 7.0规格目标包括将PCIe 6.0原始位元率(raw bit rate)由64GT/s提升到128GT/s,而在x16配置可达到512GB/s的双向传输速度。(图片来源/PCI-SIG)

PCI特别兴趣小组(Special Interest Group,SIG)上周公告PCIe 7.0规格草案进展,使电脑资料传输标準量较PCIe 5.0的8 GB/s大增4倍,目标在今年年底正式释出。

PCIe 7.0规格0.7版已经制订完成,已交由成员审查。这个版本包含成员对2024年4月的0.5版的意见,PCI SIG希望在2025年底之前完成PCIe 7.0版。

PCIe 7.0规格目标包括将PCIe 6.0原始位元率(raw bit rate)由64GT/s提升到128GT/s,而在x16配置可达到512GB/s的双向传输速度。新版规格使用PAM4(Pulse Amplitude Modulation with level4,脉冲幅度调变)信令,在维持高稳定性、低延迟性的同时也将提升能源效率,此外也会回溯相容前代规格。

PCIe 7.0的每条通道的有效吞吐量为32 GB/s,为2019年5月公布的PCIe 5.0(每条通道的有效吞吐量可达8 GB/s)的4倍。PCIe 6.0于2022年1月公布,每条通道的有效吞吐量可达约16 GB/s。

PCIe 7.0为高频宽、低延迟I/O互连技术,目标在支援资料密集的新兴应用,包括800GB Ethernet、AI/ML、云端和量子运算、超大规模资料中心、高效能运算(HPC)和军事/航太应用。